- 您现在的位置:买卖IC网 > Sheet目录250 > SDN03264C1CE1HY-60WR (Swissbit NA Inc)DRAM DDR1 256MB 200-SODIMM

�� �

�

�

�Data� Sheet�

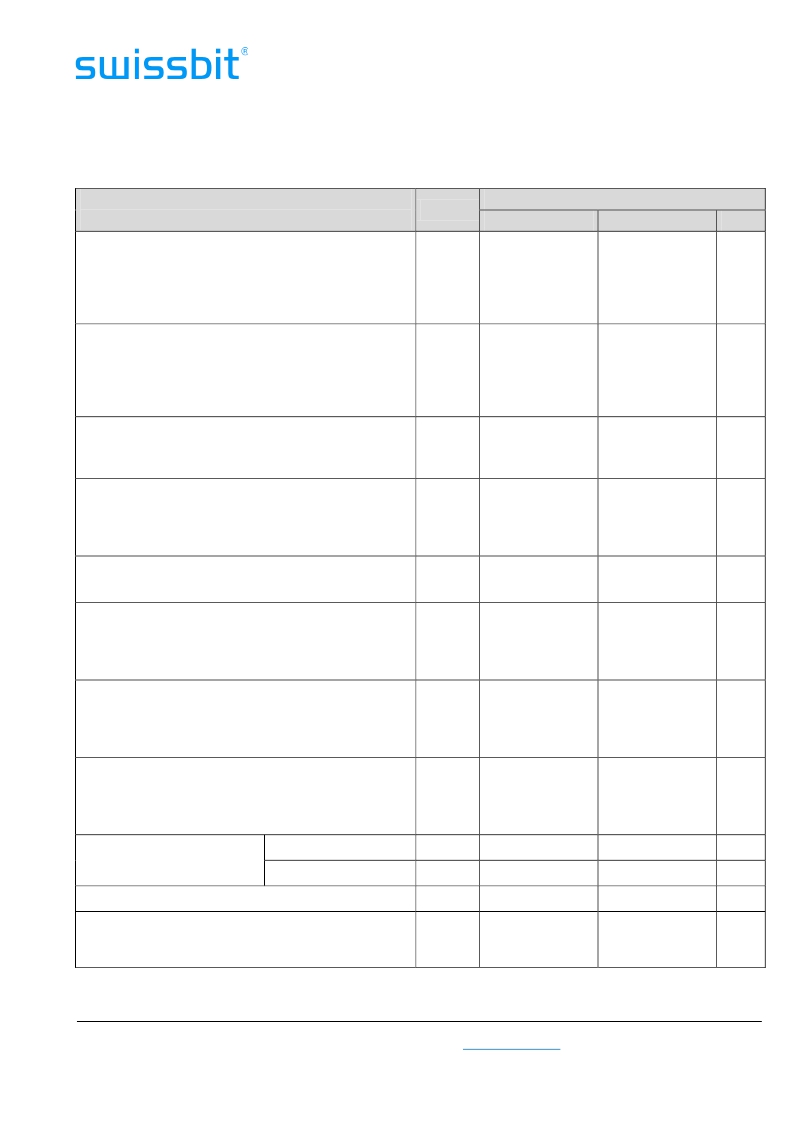

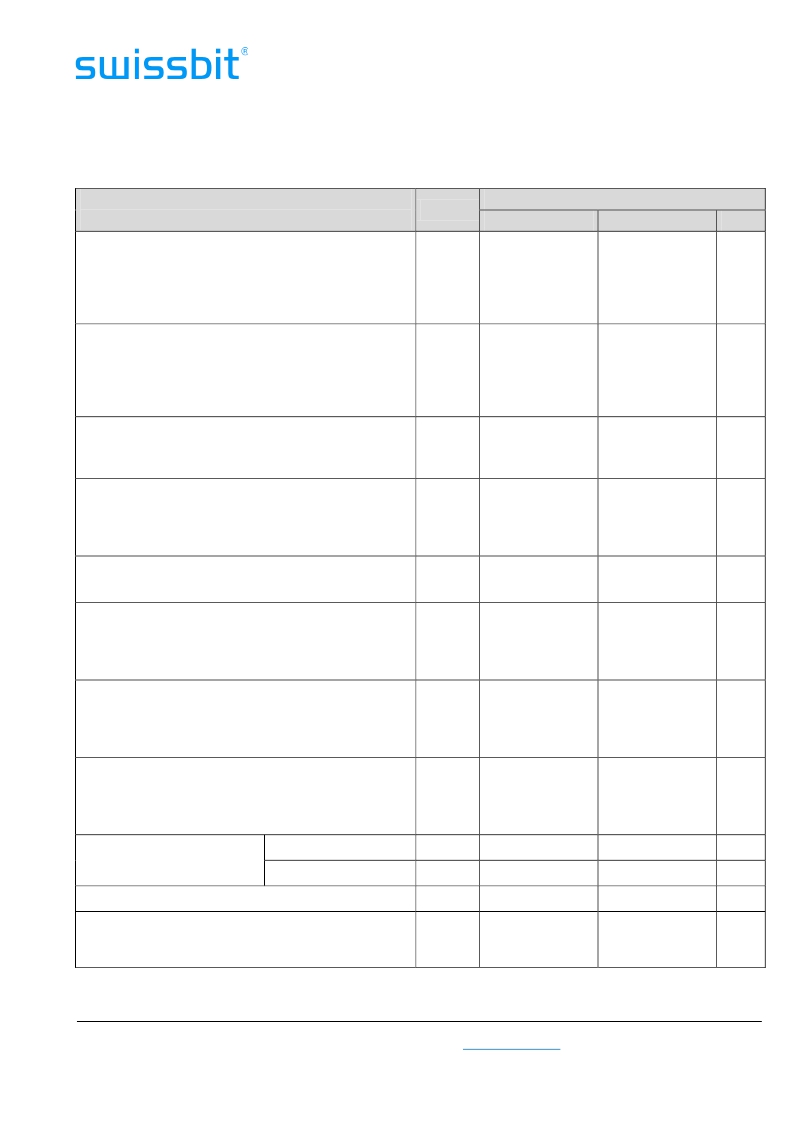

�I� DD� Specifications� AND� CONDITIONS�

�(0°C� ≤� T� A� ≤� +� 70°C;� V� DDQ� =� +2.5V� ±� 0.2V,� V� DD� =� +2.5V� ±� 0.2V)� see� Note� 1� on� Page� 9�

�Rev.1.1�

�09.06.2010�

�Parameter�

�&� Test� Condition�

�OPERATING� CURRENT� *)� :� One� device� bank;� Active-�

�Precharge;�

�Symb.�

�I� DDO�

�3200-3033�

�320�

�max.�

�2700-2533�

�260�

�Unit�

�mA�

�t� RC� =� t� RC� (Min);� t� CK� =� t� CK� (Min);� DQ,� DM� and� DQS� inputs�

�changing�

�once� per� clock� cycle;� Address� and� control� inputs�

�changing� once� every� two� clock� cycles�

�OPERATING� CURRENT� :� *)�

�One� device� bank;� Active-Read-Precharge;�

�I� DD1�

�360�

�320�

�mA�

�Burst� =� 2;� t� RC� =� t� RC� (Min);�

�t� CK� =� t� CK� (Min);I� OUT� =� 0mA;�

�Address� and� control� inputs� changing� once� per� clock�

�cycle�

�PRECHARGE� POWER-DOWN� STANDBY� CURRENT:�

�All� device� banks� idle;�

�I� DD2P�

�20�

�20�

�mA�

�Power-down� mode;�

�t� CK� =� t� CK� (Min);� CKE� =� (LOW)�

�IDLE� STANDBY� CURRENT:� CS#� =� HIGH;� All� device�

�banks� idle;�

�I� DD2F�

�92�

�92�

�mA�

�t� CK� =� t� CK� (Min);� CKE=� HIGH;� Address� and� other� control�

�inputs� changing� once� per� clock� cycle.�

�V� IN� =� V� REF� for� DQ,� DQS,� and� DM�

�ACTIVE� POWER-DOWN� STANDBY� CURRENT:� One�

�device� bank� active;� Power-down� mode;� t� CK� =� t� CK�

�I� DD3P�

�80�

�60�

�mA�

�(Min);CKE� =� LOW�

�ACTIVE� STANDBY� CURRENT:� CS#� =� HIGH;� CKE� =�

�HIGH;� One� device� bank;� Active-Precharge;� t� RC� =� t� RAS�

�I� DD3N�

�160�

�160�

�mA�

�(Max);� t� CK� =� t� CK� (Min);� DQ,� DM� and� DQS� inputs�

�changing� twice� per� clock� cycle;� Address� and� other�

�control� inputs� changing� once� per� clock� cycle�

�OPERATING� CURRENT:�

�Burst� =� 2;� Reads;� Continous� burst;� One� bank� active;�

�I� DD4R�

�540�

�380�

�mA�

�Address� and� control� inputs� changing� once� per� clock�

�cycle;� t� CK� =� t� CK� (Min);�

�I� OUT� =� 0mA�

�OPERATING� CURRENT:� Burst� =� 2;� Writes;� Continuous�

�burst;� One� device� bank� active;� Address� and� control�

�I� DD4W�

�540�

�440�

�mA�

�inputs� changing� once� per� clock� cycle;� t� CK� =� t� CK� (Min);�

�DQ,� DM,� and� DQS� inputs� changing� twice� per� clock�

�cycle�

�AUTO� REFRESH� CURRENT�

�t� RC� =� t� RC� (Min)�

�I� DD5�

�540�

�400�

�mA�

�t� RC� =� 7.8125μs�

�SELF� REFRESH� CURRENT:� CKE� ≤� 0.2V�

�OPERATING� CURRENT� *)� :� Four� device� bank� interleaving�

�READs� (BL� =4)� with� auto� precharge,� t� RC� =� t� RC� (Min);�

�I� DD5A�

�I� DD6�

�I� DD7�

�20�

�12�

�1040�

�20�

�12�

�960�

�mA�

�mA�

�mA�

�t� CK� =� t� CK� (Min);� Address� and� control� inputs� change� only� during�

�Active� READ,� or� WRITE� commands�

�*)� Value� calculated� as� one� module� rank� in� this� operating� condition,� and� all� other� module� ranks� in� IDD2P� (CKE� LOW)�

�mode.�

�Swissbit� Germany� AG�

�Wolfener� Stra?e� 36�

�D-12681� Berlin�

�Fon:� +49� (0)� 30� 93� 69� 54� -� 0�

�Fax:� +49� (0)� 30� 93� 69� 54� -� 55�

�www.swissbit.com�

�eMail:� info@swissbit.com�

�Page� 7�

�of� 12�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SE120FML,OR

CASE 8.7X7.45X3.89 ORANGE W/LOCK

SE1220FML,GM

CASE 28.17X22.27X15 GM W/LOCK

SE300FML,OR

CASE 10.80X9.85X4.87 ORANGE/LOCK

SE520FML,OR

CASE 14.85X12.15X6.85 ORG W/FOAM

SE540F,OR

CASE 14.9X12.13X9.58 OR W/FOAM

SE710CC,GM

CASE 19.75X15.53X5.413 GM

SE710FPL,OR

CASE 19.75X15.53X5.416 ORN FM/LK

SE720CC,GM

CASE 19.75X15.53X7.48 GM

相关代理商/技术参数

SDN03264C1CJ1SA-50R

制造商:SWISSBIT 功能描述:DDR SO-DIMM 256 MB 400/CL3 - Trays 制造商:SWISSBIT NA INC 功能描述:DDR1 256MB SODIMM

SDN03264C1CJ1SA-50WR

制造商:SWISSBIT 功能描述:DDR SO-DIMM 256 MB 400/CL3 - Trays

SDN03264O3BK1MT-60R

制造商:Swissbit 功能描述:602360 制造商:SWISSBIT NA INC 功能描述:DDR1 256MB SODIMM

SDN03272S4BK1MT-60R

制造商:Swissbit 功能描述:602591 制造商:SWISSBIT NA INC 功能描述:DDR1 SODIMM

SDN06464D1BE1HY-60WR

功能描述:DRAM DDR1 512MB 200-SODIMM RoHS:是 类别:存储卡,模块 >> 存储器 - 模块 系列:- 标准包装:100 系列:- 存储器类型:SDRAM 存储容量:1GB 速度:133MHz 特点:- 封装/外壳:168-DIMM

SDN06464D1BJ1SA-50R

制造商:SWISSBIT NA INC 功能描述:DDR1 512MB SODIMM

SDN06464E1C62MT-60WR

制造商:Swissbit 功能描述:TBD

SDN06464O3BK2MT-60R

制造商:Swissbit 功能描述:602368 制造商:SWISSBIT NA INC 功能描述:DDR1 512MB SODIMM